# EMBEDDED SYSTEMS VOLUME A NUMBER 1 JAN/FEB. 2008

IN THIS ISSUE:

#### Chris A. Ciufo

Small form factors in the military

#### **Duncan Young**

COTS software for embedded training

#### John Wemekamp

Brushing up motor

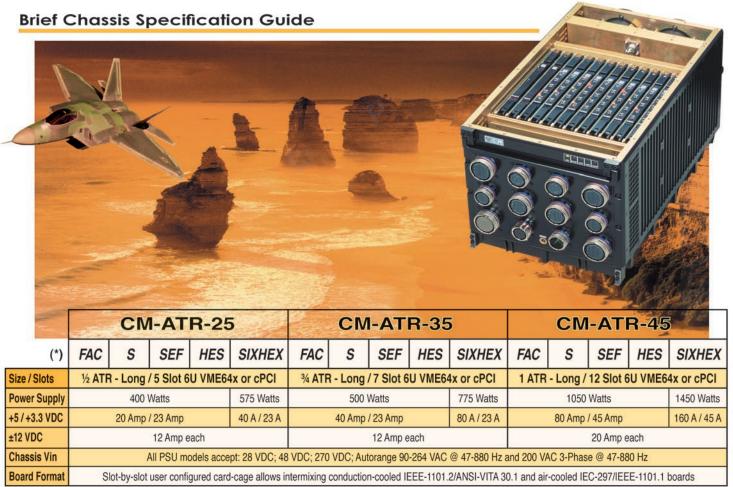

#### Discover Chassis COTS Standards with CM COMPUTER

and enter into another world with our new CM-ATR-25/35/45 Series. Up to 15 enclosure models offering outstanding Performance, oversized Power Capacity, optimum Heat Management and a wide range of Accessories & custom Options.

Decidedly well suited for critical Defense & Aerospace systems requiring premium quality that can be provided only by leading-edge technology.

(\*) Cooling Options: FAC - Flowthrough Air Cooled; \$ - Sealed; \$EF - Sealed, Extended Fins; HES - Sealed, Heat Exchanger Sidewalls; \$IXHES - Sealed, Six Heat Exchangers

All our ATR products are delivered Tested and Certified by independent authorized Labs per MIL-STD-461E & MIL-STD-810F for immediate deployment in US Navy & US Air Force military Fighters and Helicopters.

#### **Elcard™ Wireless LAN Modules** Designed for Industrial and Professional Applications

**USB-attached WLAN**

Rugged Access **Points**

- At 2.4GHz up to 11 and 54/108Mbps bandwidths

- (-40°C to 85°C and -20°C to 70°C operating)

- Rugged and shock resistant, high altitude operation

- Long term supply

- O/S support for Linux, Microsoft™ Windows™ XP/2000/NT/98SE/ME

- Dual WLAN versions available (WIB400 series)

- Evaluation kits for easy start-up

- Ranges of 1 mile+ can be reached even at 100mW Tx power with our directional antennas

- Ranges of several miles can be reached with our power amps and special antennas

- WIB250 WLAN module provides dual band 802.11g/ 2.4GHz & 802.11a/5GHz with two antenna connectors

-40°C to +85°C Operating **Temperature** Range **Versions Available**

#### AIB220 PC/104+ Cardbus

- Cardbus/PCMCIA Adapter

- Dual Type I/II or single Type III

- Linux and Win9x/2K/XP support

- 3.3V and 5V card support

TI PCI1420 chipset

Elcard USA 10849 Kinghurst, Suite 105 Houston, Texas 77099

Toll Free: 800-688-4405 Phone: 281-568-4744

Fax: 281-568-4604

Email: sales@elcard-usa.com Web: www.elcard-usa.com

# Military EMBEDDED SYSTEMS

January/February Volume 4 Number 1

#### **COLUMNS**

#### Field Intelligence

8 Off-the-shelf software enables embedded training

By Duncan Young

#### Mil Tech Insider

10 Brushing up on motor control

By John Wemekamp

#### **Crosshairs Editorial**

50 Small form factors: A new SIG in town

Stood up at last fall's ESC Boston, the SFF-SIG is ready to roll in ships, tanks, trucks, and wide-body aircraft

By Chris A. Ciufo, Editor

#### DEPARTMENTS

11,44,45 Editor's Choice Products

12 Daily Briefing: News Snippets

By Sharon Schnakenburg, Associate Editor

13 Letter to the Editor

By Greg Gicca, AdaCore

46,47,48 New Products: x86 and PowerPC SBCs

By Sharon Schnakenburg, Associate Editor

6 Advertiser Index

#### ON THE COVER:

On location at Camp Liberty, Iraq. Airman Gevoyd Little of the 447th EOD (Explosive Ordnance Disposal) operates this remote explosive detection robot looking for IEDs. A COTS device itself, the robot relies heavily on some of the Top Ten Technologies we're discussing in this issue (page 34). (U.S. Army photo taken by SSG Kevin Moses, Sr.)

#### **WEB RESOURCES**

#### Subscribe to the magazine or E-letter:

www.opensystems-publishing.com/subscriptions

#### Live industry news:

www.mil-embedded.com/news www.opensystems-publishing.com/news/submit

#### Submit new products:

www.opensystems-publishing.com/vendors/submissions/np

Published by:

#### Software: Open source COTS

14 Do-it-yourself Linux – a money pit: Commercial Linux saves time and money

By Jim Ready, MontaVista Software

18 Eclipse Europa maximizes embedded developers' productivity

By Doug Schaefer, QNX Software Systems

#### Hardware: Logic for space apps

22 Migrating FPGAs to structured ASICs in avionics to reduce SEU susceptibility

By Amr El-Ashmawi, Altera Corporation

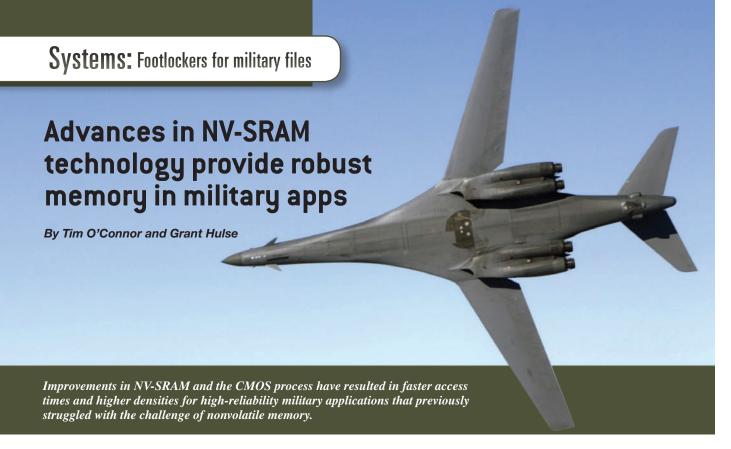

#### **Systems:** Footlockers for military files

26 Deployable mass storage systems: Bringing military applications to the front lines

By Laura Cooper, NextComputing

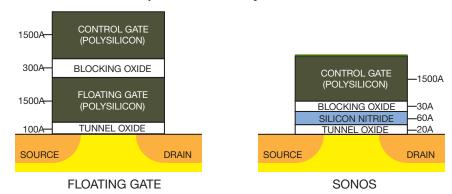

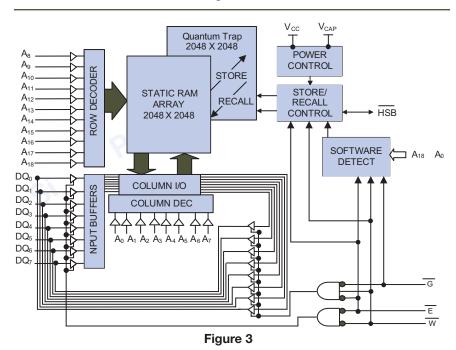

30 Advances in NV-SRAM technology provide robust memory in military apps

By Tim O'Connor and Grant Hulse, Simtek Corporation

#### Technology opinion: Top 10 trends

34 Top 10 technologies sure to affect our war fighters

By Chris A. Ciufo, Editor

39 Considerations in designing multicore systems

By Arun Subbarao, LynuxWorks

#### **Special:** Incubating COTS

40 Spin-off COTS

An interview with CCAT, the DoD's very own technology incubator that operates in a very Silicon Valley-like way

By Chris A. Ciufo, Editor

#### **E-LETTER**

www.mil-embedded.com/eletter

Heat pipe superconductors provide high-speed cooling

By Bahman Tavassoli, PhD, Advanced Thermal Solutions, Inc.

Quick, easy air cooling for VME and CompactPCI systems

By Charles Lindquist, Dawn VME Products

Mars Reconnaissance Orbiter (MRO) uses embedded technology for martian images

By John Carbone, Express Logic

**CORRECTION:** In the Nov/Dec *Crosshairs Editorial* column "MILCOM exposé," Roger Krone of Boeing was identified as President, Boeing Integrated Defense Systems (IDS); however, his correct title is President of Network & Space Systems (NSS), an IDS subsidiary reporting \$11.9 billion in earnings for 2006. (2007 figures unavailable at press time.)

All registered brands and trademarks within *Military Embedded Systems* magazine are the property of their respective owners.

© 2008 OpenSystems Publishing © 2008 Military Embedded Systems

# Annapolis Micro Systems The FPGA Systems Performance Leader

# WILDSTAR 5 for IBM Blade The Perfect Blend of Processors and FPGAs

Fully Integrated into IBM Blade Management System

Abundant Power and Cooling Ensure Maximum Performance

Made in the USA

#### **Ultimate Modularity**

From 2 to 8 Virtex 5 FPGA/Memory Modules Input / Output Modules Include: Quad 130 MSps thru Quad 500 MSps A/D 1.5 GSps thru 2.2 GSps, Quad 600 MSps A/D Dual 1.5 GSps thru 4.0 GSps D/A Infiniband, 10 G Ethernet, FC4, SFPDP

#### Direct Seamless Connections with no Data Reduction

Between External Sensors and FPGAs

Between FPGAs and Processors over IB or 10GE Backplane

Between FPGAs and Standard Output Modules

190 Admiral Cochrane Drive, Suite 130, Annapolis, Maryland USA 21401 wfinfo@annapmicro.com (410) 841-2514 www.annapmicro.com

#### OpenSystems Publishing

#### Advertising/Business Office

30233 Jefferson Avenue St. Clair Shores, MI 48082

Tel: 586-415-6500 Fax: 586-415-4882

**Vice President Marketing & Sales**

Patrick Hopper

phopper@opensystems-publishing.com

**Business Manager**

Karen Layman

#### Sales Group

**Dennis Dovle**

Senior Account Manager

ddoyle@opensystems-publishing.com

Tom Varcie

Senior Account Manager

tvarcie@opensystems-publishing.com

**Doug Cordier**

**Account Manager**

dcordier@opensystems-publishing.com

Andrea Stabile

Advertising/Marketing Coordinator

astabile@opensystems-publishing.com

**Christine Long** E-marketing Manager

clong@opensystems-publishing.com

#### **Regional Sales Managers**

Jerry Bleich

**New England**

jbleich@opensystems-publishing.com

**Ernest Godsey**

**Central and Mountain States**

egodsey@opensystems-publishing.com

Barbara Quinlan

Midwest/Southwest

bquinlan@opensystems-publishing.com

Denis Seger

Southern California

dseger@opensystems-publishing.com

Sydele Starr Northern California sydele@pacbell.net

**Ron Taylor**

East Coast/Mid Atlantic

rtaylor@opensystems-publishing.com

#### **International Sales**

Dan Aronovic

Account Manager - Israel

daronovic@opensystems-publishing.com

Sam Fan

Account Manager - Asia

sfan@opensystems-publishing.com

#### **Reprints and PDFs**

Nan Lamade: 800-259-0470 • mesreprints@opensystems-publishing.com

#### ADVERTISER INFORMATION

#### Page Advertiser/Product description

- 11 ACCES I/O Products, Inc. - The source for all your I/O needs

- 31 ACT/Technico - Embedded sub-systems

- 21 Acumen Instruments - DataBridge SDR-CF

- 24 Advantech Corporation - Total rugged solutions for Mil

- 20 Alphi Technology Corporation - Modular solutions

- 5 Annapolis Micro Systems, Inc. - Wildstar 5 for IBM blade

- 42 Avionics - Five reasons to register now

- 26 BMC Communications - Protocols converter

- 2 CM Computer - Discover chassis COTS standard

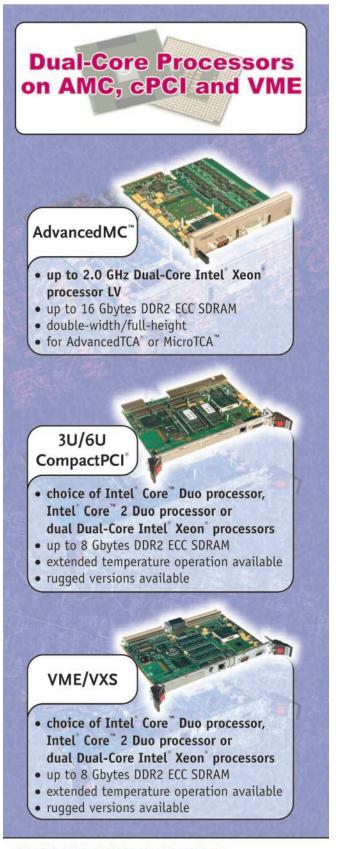

- 19 Concurrent Technologies, Inc. – Dual-core processors

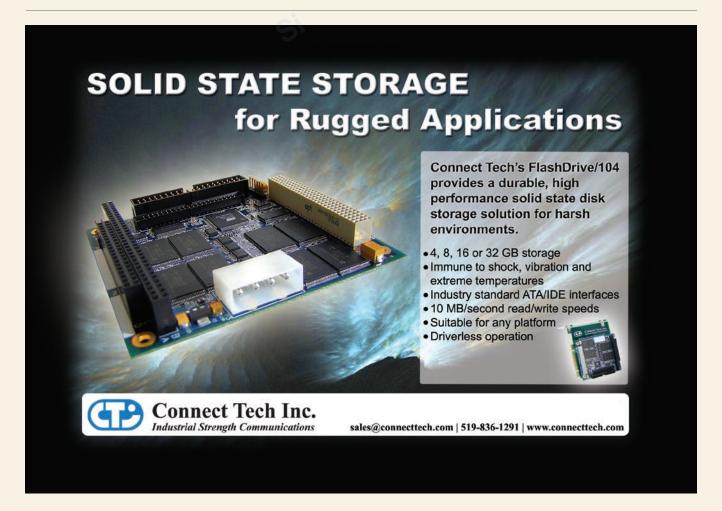

- 41 Connect Tech Inc. - Solid-state storage

- 52 CWCEC: Data Communications - Your data is critical

- 15 Excalibur Systems, Inc. - Dense

- 51 GE Fanuc Intelligent Platforms, Inc. - AXISLite

- 7 Hypertronics - Unite

- 3 Microbus Inc - Elcard wireless LAN modules

- 43 Military and Aerospace Electronics - Under the COTS Umbrella

- 16 MPL AG - You need

- 37 Performance Technologies - What's on your radar

- 27 Phoenix International - Mission critical

- 33 Schroff, a brand of Pentair Electronic Packaging - When your mission is critical

- 49 Super Talent Technologies - Reinventing storage

- 21 TEWS Technologies LLC - COTS I/O solutions

- 23 Tri-M Systems Inc. - Tri-M Engineering

- 25 Tri-M Systems Inc. - Tri-M Systems

- 38 VersaLogic Corp. - The only thing missing is the lead

- 9 VMETRO - The sky is the limit

- White Electronic Designs Advanced Microelectronics solutions 35

- 28 Winchester Electronics - Power connector solutions

## Military embedded systems

OPENSYSTEMS PUBLICAT

#### Military and Aerospace Group

- DSP-FPGA.com Resource Guide

- DSP-FPGA.com

- ш. DSP-FPGA.com E-letter

- ш. Military Embedded Systems

- Military Embedded Systems E-letter

- PC/104 and Small Form Factors

- PC/104 and Small Form Factors E-letter

- PC/104 and Small Form Factors Resource Guide

- VME and Critical Systems

- VME and Critical Systems E-letter

Group Editorial Director Chris A. Ciufo

cciufo@opensystems-publishing.com

Terri Thorson Senior Editor (columns)

tthorson@opensystems-publishing.com

**Associate Editor** Sharon Schnakenburg

sschnakenburg@opensystems-publishing.com

Assistant Editor

Robin DiPerna Hermann Strass

**European Representative**

hstrass@opensystems-publishing.com

Senior Web Developer Web Content Specialist C eative Director

Matt Avella Steph Sweet David Diomede Art Director

Konrad Witte

**Graphic Coordinator** Sandy Dionisio Circulation/Office Manager

Phyllis Thompson subscriptions@opensystems-publishing.com

#### OpenSystems Publishing

Editorial/Production office:

16872 E. Ave of the Fountains, Ste 203, Fountain Hills, AZ 85268

Tel: 480-967-5581 Fax: 480-837-6466 Website: www.opensystems-publishing.com

Publishers John Black, Michael Hopper, Wayne Kristoff

Vice President Editorial Rosemary Kristoff

#### Communications Group

Editorial Director Joe Pavlat Assistant Managing Editor Senior Editor (columns) Technology Editor

Anne Fisher Terri Thorson Curt Schwaderer

European Representative Hermann Strass Senior Designer Joann Toth

#### Embedded and Test & Analysis Group

**Editorial Director Editorial Director** Senior Associate Editor **Special Projects Editor European Representative**

Jerry Gipper Don Dingee Jennifer Hesse **Bob Stasonis** Hermann Strass

ISSN: Print 1557-3222

Military Embedded Systems (USPS 019-288) is published eight times a year (January/February, March/April, May, June, July/August, September, October, November/December) by OpenSystems Publishing LLC, 30233 Jefferson Avenue, St. Clair Shores, MI 48082.

Subscriptions are free to persons interested in the design or promotion of Military Embedded Systems. For others inside the US and Canada, subscriptions are \$28/year. For 1st class delivery outside the US and Canada, subscriptions are \$50/ year (advance payment in US funds required).

Canada: Publication agreement number 40048627 Return address WDS, Station A PO Box 54, Windsor, ON N9A 615

POSTMASTER: Send address changes to *Military Embedded Systems* 16872 E. Ave of the Fountains, Ste 203, Fountain Hills, AZ 85268

#### HIGH DENSITY AND RELIABILITY

In designing high density military applications, it is critical that the hardware components provide environmental immunity united with connection reliability to meet the demanding requirements for signal integrity, consistent resistance and operational performance in extreme conditions. Hypertronics HyperGrid<sup>TM</sup> compression mount connectors adhere to any footprint down to 0.4mm pitch and are suitable for high speed microwave MMIC, flat panel displays, flexible cables, printed circuit and parallel boards, and RoHS compliant solderless, multi-termination connections.

#### **HyperGrid Features**

Micro Miniature Contacts Low Contact Self Inductance Up to 37 GHz Speeds Modular Design/Custom Footprints 100,000+ Mating Cycles

#### Benefits

Reduced Weight and Space Superior Signal Integrity Exceptional AC Performance Fully Adaptable Z-Height and Form Factors Robust Enough for Dynamic Environments

Hypertronics interconnect solutions are choice of engineers worldwide for mission critical systems.

www.hypertronics.com/unite

HYPERTRONICS: WHEN FAILURE IS NOT AN OPTION

#### Field Intelligence

#### Off-the-shelf software enables embedded training

Training has always been a top priority for the armed forces, and much of their time is spent honing their preparedness to deal with conflicts and operate the complex and sophisticated weapons platforms at their disposal. Training takes many forms including classroom, procedural, simulated, and embedded through to the live exercise. Each type is designed to prepare for every eventuality from the instinctive reaction to the intuitive reasoning required to deal with a real-life scenario. This need is reflected in the design of many weapons platforms where systems are now being architected so that their human interfaces (screens, keyboards, and pointing devices) are accessible both to live sensors and weapons and to the synthetically generated scenarios of embedded training.

Being able to effectively operate each of the various subsystems making up a weapons platform is arguably the most essential training that is required. The skills to operate a complex weapon or Naval tactical console cannot be taught in the classroom environment alone and need to be reinforced regularly, which can only be achieved using a live platform. Typically such a training system will have four components:

- Scene simulator

- Scene builder

- Scenarios

- Hardware and integration

The scene simulator determines how the training system will display the scene to the trainee. It will offer a view of the scene as if it were being played back through a particular sensor type, for example, as perceived by a radar or an electro-optical or infrared sensor. The scene simulator also plays the scenario, moving objects and background as the training scenario plays out, reacting to inputs from the trainee and, optionally an instructor. Most systems will offer the ability to record operator inputs and to rerun any part of the exercise at the trainee's or instructor's discretion.

A key part of any training system is achieving a level of realism of the background and objects in order to fully engage the trainee in the exercise. A scene builder is the package that is used to create the objects that are to be displayed. Objects may be anything from people, weapons platforms, airplanes, trees, hills, houses, and so on. Objects can be defined in three dimensions and rules created for their movements and interaction with other objects. Many packages will include a library of objects that can be reused or modified as required.

Figure 1

A training scenario is the sequence of events that the training system plays out to the trainee. Scenarios are built offline for each training session to meet whatever the objectives may be. A platform will usually have a number of canned scenarios available for regular training exercises.

Because embedded training takes place on the same equipment as is normally deployed in live operations, the training system must have independent access to any display monitors and data entry devices such as keyboards, pointers, push buttons, and so on.

More modern systems have been designed to accommodate this, but older legacy systems will require extensive modification to support the addition of an embedded training system. Often such

a system is PC-based with specialized interfaces for the data entry devices plus a high-performance graphics accelerator for display. Of course, training exercises could be embedded within a vehicle's overall operational software package, obviating the need for any additional hardware dedicated to training. However, this brings with it concerns for safety and security unless the training is very robustly partitioned from the operational software; firing live missiles or making compromising radio emissions must be avoided at all costs. It is also difficult and more costly to just update the training package as the entire operational software package may need to be requalified if any part of it is modified.

An example of an embeddable training package that can be used to introduce realistic training exercises into existing platforms is the SIVET-SE produced by GE Fanuc. It can be hosted on most high-performance, embeddable PCs from commercial grade through to full military specification and is targeted primarily toward the simulation of electro-optical sensor types. Figure 1 illustrates a typical workstation in an armored vehicle that could be supported by the embedded training concepts of SIVET-SE.

Training is an essential ingredient of every type of system used by the armed forces. While the eventual solution will be to equip every platform with training embedded from within the operational software, there are many legacy platforms in need of life extension where the availability of proven, off-the-shelf tools and hardware makes the provision of embedded training an economic reality. As these products become more sophisticated through continual product investment, they will converge with wholly embedded software, extending and strengthening this important COTS software market segment.

To learn more, e-mail Duncan Young at young.duncan1@btinternet.com.

# The sky is the limit

Sensors, Receivers, etc.

Analog or

Digital Input

FPGA/DSP Processing

Analog or

Digital Output

Presentation, Transmitters, etc.

# with FPGA-based DSP solutions for Electronic Warfare & ISR systems

#### FPGA-based Analog I/O:

- 3 GSPS ADC (AD3000)

- Dual 1.5 GSPS ADC (AD1500)

- Dual 105 MSPS ADC (ADC-MOD1)

- Dual 210 MSPS DAC (DAC-MOD1)

#### FPGA-based Digital I/O:

- Camera Link (CAML-MOD3)

- LVDS (LVDS-MOD3 & LVDS-MOD4)

- sFPDP, FPDP & FPDP-II (SFM & DPIO2)

- RS485/422 (RS485-MOD2)

- 10 Gb Ethernet (V1020)

- Fiber Optic (PMC-FPGA03F)

#### High-Performance Real-Time Processing Solutions:

- VXS Processor with Freescale MPC8641D and Dual Xilinx® Virtex™-5 FPGAs (Phoenix VPF2)

- VXS Carrier with Dual XMC sites (Phoenix M6000)

- VXS Processor with Dual Virtex<sup>™</sup>-4 FPGAs (MM-1500 & MM-1550)

- VXS Recording Engine (Vortex VXS)

- VXS Switch Card (Phoenix CSW1)

- VPX Processor with Dual Virtex<sup>™</sup>-4 FPGAs (MM-1600 & MM-1650)

**Buffer Memory Nodes**

Xilinx Virtex-5 based XMC/PMCs

Embedded Computing - Data Recorders & Rugged Storage - Bus & Protocol Analyzers

For more information, please visit http://www.vmetro.com or call (281) 584-0728

#### Mil Tech Insider

#### Brushing up on motor control

By John Wemekamp

of motor-driven components such as a turret, gun, hatches, fans, pumps, ammunition handling, and many others. The recent advances in high-power electric motion control and the introduction of hybrid electric drive to fighting vehicles arguably deserves a high placing in the top 10 list of technologies for the war fighter for speed of reaction, reduction of workload, reliability, and remarkable power density.

The majority of today's fighting vehicles use hydraulics for actuating their mechanical systems. Typically operating at 3,000 to 5,000 psi, hydraulics are prone to leakage and difficult to repair and maintain. In addition, hydraulic pumps, piping, and actuators are bulky and heavy compared to the latest generation of motor-driven subsystems that is set to replace them in the future. Whether the function to be performed is a simple, single-axis operation such as closing a hatch or the much more complex sequence of moves of an autoloader, all closed-loop servo systems share common control requirements to vary torque, acceleration, velocity, and position in order to accomplish their specific functions. Such servo systems use a controller/amplifier that modulates high-voltage dc (up to 610 V) to one or a number of motors to create the motion required. The controller will have a number of inputs such as analog, resolver, or encoder to sense position or velocity to close the loop.

Modern fighting vehicles have an integrated vetronics architecture supporting all the functions necessary to drive and control them. Based on redundant Ethernet or CANbus architectures, bused vetronics systems save on the mass of discrete point-to-point cabling that would otherwise be needed. All functions from external lighting to maneuvering the vehicle or rotating the turret will be transmitted over the vetronics bus as a series of commands to remote controllers located adjacent to the function to be performed. Motor controllers, like other vehicle functions, receive their commands via the vetronics bus. They are most often implemented as Line Replaceable Units (LRUs), complete with considerable intelligence to perform the servo function on command, in addition to handling background diagnostics and local error detection.

Controllers come in a range of types, controlling from one to many axes of movement from one LRU. For a complex piece of equipment such as an autoloader, commands received via the vetronics bus will choreograph a sequence of controlled motions from many motors to select, for example, the required type of ammunition from a dispenser, arm it, move it into position, and load it ready for firing. To accomplish this level of complexity, some controllers are programmable, their specific set of functions being created during development using modeling and simulation tools such as MATLAB and Simulink.

In ground-based fighting vehicles these mechanical components are often large and heavy, requiring a great deal of power to move and position them accurately and safely. Since vehicle weight and size are such critical parameters, demands for power to move heavy components

must be traded against weight and physical size of the servo system. The controller is a key element and continuous development is targeted to reduce weight, power, and size of the controller and motors. The success of these efforts can be judged from Table 1, which compares the physical size and power delivery of a typical motor controller with a conduction-cooled VMEbus power supply module.

power density.

This level of power density exceeds the capacity of conventional air-or conductioncooling techniques, requiring both exacting thermal design of the LRU and its components and the employment of liquid cooling. This form of cooling is used in a range of motor controllers produced by Curtiss-Wright Controls Embedded Computing (CWCEC). Designed for a

|                      | Dimensions<br>(inches) | Volume<br>(cubic inches) | Continuous<br>power delivery<br>(watts) | Power density<br>(W/cubic inch) |

|----------------------|------------------------|--------------------------|-----------------------------------------|---------------------------------|

| VMEbus power module  | 6.2 x 9.3 x 1.6        | 92.3                     | 750                                     | 8.13                            |

| Controller/amplifier | 5.8 x 8.8 x 8          | 408                      | 6,000                                   | 14.7                            |

Table 1

wide range of high-power, vehicle-based motion control applications, the internal construction and cooling of an example controller are shown in Figure 1.

Figure 1

The precise control of the machinery's motion might not be perceived to be as glamorous as a cooperative, networked command and control system or the multiple compute nodes of a synthetic aperture radar processor, but motor control truly stretches its designers and technology to the limits. As a result of this evolution of compact motor controllers, size and weight of modern fighting vehicles will continue to be reduced. This will enable them to be more effective platforms, carrying greater payloads of troops, command and control systems, sensors, weapons, and self-protection systems.

For more information, e-mail John at john.wemekamp@curtisswright.com.

#### **Editor's Choice Product**

#### Portable, rugged 3U RAID

Disk drives are so inexpensive these days — under \$1 per GB — that we're saving everything instead of deleting it. But in deployed platforms and systems, where collecting and storing the data is the whole point, it's not enough just to have beaucoup storage. One needs assurances of reliable data storage. That's the point behind Phoenix International's RPC12 SAS/SATA II 3U RAID system: ruggedness, reliability, portability. Housing up to 12 HDDs in carriers, the 3U (5.25") system has redundancy and ruggedness built in everywhere you look.

Capable of withstanding 60 g shock at 2 ms, operating over 5 °C to 60 °C (even more with sealed drives), and up to 40,000 feet with sealed HDDs, this baby's in it for the long ride. It accommodates RAID 0, 1, 3, 5, 10, 50, NRAID, and JBOD as well as dual hot-swap PSUs and cooling fans. Host interfaces include 2 or 4 Gbps Fibre Channel, serial attached SCSI, or iSCSI. Input voltage ranges from 40 to 440 Hz, and from 90 to 240 VAC. As for software, the unit interfaces to Windows, Linux, and UNIX and includes a management GUI and failover software.

Phoenix International • www.phenxint.com • RSC# 35575

### Daily Briefing: News Snippets

By Sharon Schnakenburg, Associate Editor

www.mil-embedded.com/dailybriefing

#### **Australian and U.S. governments** give each other space

... Or rather, the Australian and U.S governments are about to get into the same space: The U.S. Air Force has authorized Boeing to build a sixth Wideband Global SATCOM (WGS), and the Commonwealth of Australia is funding the endeavor as part of an agreement between the two nations. In exchange, the Australian Defence Force gains worldwide WGS service access. The new WGS satellite will be a Block II version of the 702 model spacecraft, supporting Radio Frequency (RF) bypass data rates of up to 311 Mbps (200x faster than typical DSL or cable connections).

#### Patents: Yours, mine, or ours?

In the wake of a continuing barrage of technology patent disputes, some contentions are finally getting resolved: Artesyn Technologies – recently acquired by Emerson Network Power, as was Motorola's Embedded Communications Computing group – offered a successful defense on most of the 82 patent infringement claims lodged by Power-One, Inc. surrounding 4 of Artesyn's patents. A Texas jury found only one patent infringement on a product never sold by Artesyn, and the jury determined that infringement was unintentional. A fee of \$100 in damages may be awarded to Power-One, Emerson reports.

#### Green Hills and its Padded Cell

Is security the problem or the remedy? "Many people believe that hypervisors are the solution to security problems. But existing hypervisors actually make security problems worse by providing another avenue for attack," says Green Hills Software founder and CEO Dan O'Dowd. Accordingly, Green Hills has announced what it calls "the world's first secure hypervisor" or the Padded Cell Secure Hypervisor, which operates on top of the company's EAL6+ compliant INTEGRITY separation kernel and compartmentalizes and virtualizes guest operating systems. Additionally, it implements separation among virtual machines: Its virtualization software operates as an application and therefore cannot circumvent the separation kernel's security policies.

#### **Increased optimization in a** reduced size

It's all in a day's work – or at least in a day's announcement – for Intel, which unveiled 16 new lead- and halogen-free products at the International 2008 Consumer Electronics Show held in Las Vegas, Nevada. Among the offerings announced are Intel's first 45nm processors for tucking inside Intel Centrino Processor Technology based laptops. The chips leverage Intel's new transistor formula and increase PC speed, prolong battery life, reduce power consumption, and are available in smaller packages.

#### VITA's VPX scores with ANSI

Nearly four years in the making, VITA's VPX base standard (ANSI/VITA 46.0-2007) and its "dot standard" VMEbus Signal Mapping for VPX (ANSI/VITA 46.1-2007) have received American National Standards Institute (ANSI) ratification. VITA 46.0 describes the full suite of VPX dot standards and VPX's physical features. Meanwhile, VITA 46.1 enables legacy and latestgeneration VMEbus technology to converge under VPX. The VPX backplane standard accommodates several switch fabric protocols including PCI Express, Serial RapidIO, and GbE, among others.

#### **Double duty** for new CWCEC **Senior VP**

Multitasking is required at most jobs these days ... particularly if you're Curtiss-Wright Controls' new Senior VP Tom Quinly, who is also continuing in his role as president of the company's Embedded Computing Division. Quinly received his recent

promotion to SVP, according to Curtiss-Wright Controls president David Adams, because of his strong performance within the company. Quinly has 25 years of experience in the defense industry and became part of Curtiss-Wright Controls with its acquisition of his employer, Dy4, in 2004.

#### Savi enters 'green' scene

Not only is "green" a growing trend in the U.S. and Europe, it's also hot in Kuwait, as Lockheed Martin subsidiary Savi Technology is proving. Savi's engineers recently installed Radio Frequency Identification (RFID) signposts and solar panels at a key U.S. Army supply depot in Kuwait. The new technology reportedly reduces costs, is environmentally friendly, and removes any need for electrical infrastructure installation in remote areas. Plans are also in the works with the U.S. DoD to bring solar-powered technology to additional Middle Eastern regions, Savi reports.

#### New iRobots to provide a theater of operations

More war fighters can stay out of harm's way, thanks to the U.S. Army's new \$286 million xBot contract with iRobot Corp. The Indefinite-Delivery, Indefinite-Quantity (IDIQ) contract stipulates that the Army can acquire up to 3,000 military robots, along with training, spare parts, and repair services within the next five years. As the new robots will largely be deployed for mission-

critical general infantry force purposes, the contract indicates a departure from the Army's earlier strategy to only deploy robots to Explosive Ordnance Device (EOD) specialists.

#### **RTI and Northrop Grumman: CLIP**ping out military data issues

Northrop Grumman and Real-Time Innovations (RTI) recently joined forces to "CLIP" a new DDS-compliant interface into the U.S. Navy and Air Force Common Link Integration Processing (CLIP) system. Aimed at solving inherent incompatibility between the two branches' Tactical Data Links (TDLs), CLIP enables legacy platforms connection to IP-based systems. It also enables TDL processing for platforms without their own data link via bridging a new TDL radio/terminal to the legacy mission computer's software. CLIP's new DDS interface is Net-Centric Enterprise Solutions for Interoperability (NESI) compliant and purported to ease TDL integration.

#### **Chassis Plans partners up**

Some say "less is more," but Chassis Plans may beg to differ. The mission-critical COTS and custom computer systems manufacturer recently earned the title of Microsoft Certified Partner, which enables

its access to additional training, software licensing, and technical support

channels. Steve Travis, Director of Program Management at Chassis Plans, says, "Our customers can't afford downtime with these systems installed in Iraq and other mission-critical arenas. Gaining Microsoft Certified partner status fits within our ISO:9001 plan and shows our customers our commitment to quality in the products we ship them."

#### Fast path to DO-178B certification

Companies laboring for DO-178B certification might find a speedier route if they use DDC-I's mixed-language development environment OpenArbor, which now supports the FAA-certified LynuxWorks LynxOS-178 RTOS. Any developers utilizing OpenArbor in C, Ada, and Embedded C++ (EC++) or any combination thereof can reach DO-178B Level A certification by using the RTOS to deploy their mission-critical applications.

#### Cell phone-like device protects soldiers from chemical threats

General Dynamics has chosen biological subsystems and sensor chips producer Sionex Corporation to supply Differential Mobility Spectrometry (DMS) technology for use in its JUNO "cell phone-style interface" chemical detector. JUNO is part of a contract between General Dynamics and the U.S. DoD under the Joint Chemical Agent Detector (JCAD) program's Increment 2. JUNO can simultaneously monitor levels of exposure to chemical warfare agents, nontraditional agents, and toxic industrial chemicals. It also lets users know when decontamination efforts are successful.

#### LETTER TO THE EDITOR

Dear Editor,

Thank you for your article on the continued health of the Ada language and its market for safety-critical systems. In the Sept/Oct 2007 issue of *Military* Embedded Systems and your editorial, The "A's" have it, you mentioned new support for Wind River's VxWorks 653 Platform. AdaCore has supported this platform since 2002 when GNAT Pro was selected for both the KC-767 and C-130 AMP projects. This is the GNAT Pro High-Integrity Edition for DO-178B, which has been used to successfully develop certified avionics systems on multiple aircraft, and which continues to be used in this safety-critical domain. The High-Integrity Edition for DO-178B contains a certifiable runtime system, a full ARINC-653 API, along with various support tools to aid in safety-critical certification efforts. We are delighted to see the market for Ada and safetycritical systems continuing to expand with new vendors entering the market.

Sincerely, Greg Gicca AdaCore Director of Safety and Security Product Marketing

Companies that haven't clearly understood the high life-cycle costs of in-house RTOS development typically find themselves victims of the "software money pit." But in the buy-versus-make RTOS decision, commercial Linux clearly provides cost and complexity advantages versus the do-it-yourself Linux alternative.

For the past 25 years, engineering organizations developing software for embedded devices have become embroiled in the buy-versus-build decision for Real-Time Operating Systems (RTOSs). At the core of the debate is the emergence of commercial RTOSs, providing a complete system off-the-shelf and eliminating the need to write an RTOS system in-house.

However, these COTS RTOSs carried a tidy price, and some entrants into the embedded market view them as more expensive than writing their own RTOS in-house.

However, most companies who choose to develop their own RTOS in-house have learned that there are many cost considerations that lie beneath the surface. Many organizations haven't fully understood the life-cycle costs encountered in developing an RTOS in-house, and most have learned the hard way about the development process costs involved. Thus, the in-house alternative often results in a "software money pit" where engineers start down the in-house development road, then pick up cost after cost until they

realize it has become very expensive. By then, though, it is difficult to stop since so much has been invested.

Linux, however, is one RTOS that has established itself as the preferred Operating System (OS) for a wide variety of embedded devices. It too comes in two forms: Commercial and in-house. As time has proven, commercial embedded Linux has many advantages that developers should consider over building an in-house version of embedded Linux. An understanding of such considerations removes most of the debate as to whether or not to build in-house or purchase a commercial Linux package. Important factors developers need to consider include "obvious" and "hidden" costs, along with the rising open-source complexity issues that affect the in-house versus COTS Linux equation.

#### The explosion of software content in devices

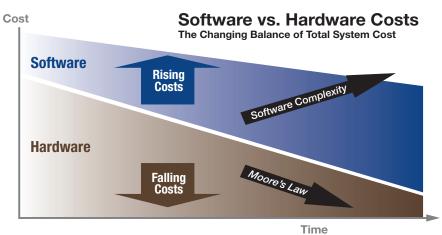

There are two dimensions of rapid expansion in the embedded system world that underlie this move to Linux over traditional RTOSs:

- The growth of new and complex product categories

- The growth of requirements for the system software in the embedded device itself

A case in point: A military manufacturer that previously dealt with small amounts of firmware needs to develop a whole new range of products based on a complete OS environment with multi-programming, TCP/IP connectivity, built-in security, and more. Consequently, this manufacturer suddenly finds its product teams forced to make decisions about the development and adoption of millions of lines of OS software into their product lines. With such an explosion in internal costs and in the complexity of product design and development, there is the risk of a software crisis throughout the technology product industries (See Figure 1). This is especially true in the embedded military market, where there is an increasing amount of scrutiny over cost, complexity, and time-to-market issues. Other considerations include:

- 1. The need for such system software cuts across a large number of different product organizations and teams. The external competitive situation doesn't tolerate a high cost structure for system software. Current budget constraints will not support the in-house teams formerly maintained; a company's engineering resources must focus on value-added technology to remain competitive.

- 2. The royalty component of current off-the-shelf system software in the cost of goods is large and impacts corporate margins.

- 3. The selection of a common, strategic system software platform will help a company avoid getting mired in a multiplicity of alternatives, each with a high cost structure and no overall leverage. Industry experience shows that disparate platforms inflate costs and increase product development cycles.

Figure 1

The growing popularity of embedded Linux as an alternative to traditional RTOSs is evident from the tens of millions of electronic devices that have already shipped with Linux as their OS. Ironically, however, even within organizations facing increasing pressure to produce softwareintensive products with high functionality and quality requirements, as well as strong schedule pressure, the temptation to implement Do-It-Yourself (DIY) Linux remains alive and well, as opposed to off-the-shelf Linux, and development costs are a key factor – both obvious and hidden.

#### The "obvious" development costs

There are many processes and costs to understand in embedded Linux that are native to both in-house and commercial implementations; however, the difference is that these factors are typically included in the cost of commercial packages:

It is not unusual for an embedded Linux or Linux distribution in general to comprise more than 30 million lines of source code.

- The code base can comprise 19 or more different, unsynchronized and non-integrated code repositories.

- The code base often changes daily.

- Many large companies use a wide range of embedded processor architectures requiring support for as many as 24 microprocessor architectures and their variants, and more than 100 hardware platforms.

- Multiple host computing environments and various revisions must be supported (such as Windows and Solaris, among others).

- The time to construct, test, and deliver an initial distribution can easily reach more than 30 development years (not including the ongoing maintenance, minor enhancements, or support time), which easily amounts to a cost in the seven-figure range. The ongoing maintenance, addition of minor enhancements, support, and the building of a development infrastructure also add significant ongoing cost.

Most commercial Linux distributions not only take these factors into account, but also have tools, resources, and expertise to help address them, making it an even more viable option for developers than downloading from kernel.org and building their own flavor. Considering that the typical cost of outfitting a mid-sized development team (~10 engineers) with a commercial distribution can be well under \$100,000, the cost savings over a seven-figure in-house development effort reflect a real bargain.

#### The "hidden" development costs

In addition to the more "obvious" development activities, there are numerous "hidden" or often overlooked efforts that are essential to a successful development effort. Efforts involved in in-house development include:

■ The development of a comprehensive Testing/QA capability. Test suites need to be developed for the OS itself and the wide range of I/O devices present, especially in SoC devices. (A typical SoC for a mobile device has 20-30 complex I/O devices built in – all these need to be tested.) The physical infrastructure to host all the reference boards for each architecture needs to be developed and deployed.

- The creation of a build computing environment that is efficient and capable of turning the build around as quickly as possible (hours not days); otherwise, the build process itself becomes a bottleneck in the overall project development flow.

- Tool development: cross debuggers, memory leak detection tools, performance-tuning tools, kernelaware debuggers, and the list continues. Rarely are developmental dollars allocated to tool development, since most of the money had to be invested in developing the kernel itself.

- Training course material and course delivery. The Linux system is quite large and functional. Developers need training on its programming model, device driver structure, and development tools in order to be productive quickly.

These additional "hidden" costs can also affect delays, which can be quite costly. In fact, a December 2007 Embedded Market Forecasters report states that the average cost for each month of design delay is \$386,250 assuming that the average cost per engineer is \$150,000 per year and an industry average of 30.9 developers per project (www.embeddedforecast.com).

#### Process development, the "new complexity," and costs

The process development costs that Linux DIY projects incur are another cost consideration in the make-versus-build equation. It's clear that without the proper "Linux/ open source-aware" processes in place, the development schedule and product quality will both suffer the potential for skyrocketing costs and/or outright failure.

Unlike a traditional in-house development process where the overall procedure could be strictly controlled from start to finish, in-house embedded Linux development begins with a largely uncontrolled process: open source. While an individual company might actually contribute to a particular open source project, by no means can that company totally control the process - it can only hope to influence and participate. For example, the rate of change of Linux from release to release can vary, from minor bug fixes and modest new feature enhancements to wholesale changes in underlying subsystems, introducing new capabilities as well as new instabilities and bugs.

The sheer volume of these changes can be daunting. Consider tracking the activities around an individual architecture for Linux, MIPS for example. To keep abreast of the changes occurring on a daily basis, a developer needs to monitor the email traffic of 11 different and unsynchronized open source projects: kernel.org, the core home of the Linux kernel; the gcc and glibc projects (the core tool chain and libraries from FSF at fsf.org); and at least nine other components that would typically comprise a useable Linux development environment.

Kernel.org itself may have up to 5,000 messages a day with 1,000 of these being patches that need to be evaluated and possibly applied to the source base. Simply ignoring the traffic, figuring that the system in use seems to be working well enough, can lead to disastrous consequences later. For example, a recent security patch that took all of 13 lines of code to implement against an embedded Linux system would have taken more than 800k lines of source patches to implement if the previous trail

of patches had been ignored. It's a classic case of pay now or really pay later.

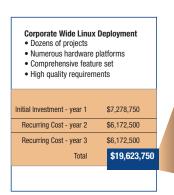

#### Adding it all up

All of the aforementioned factors combine to make developing a DIY embedded Linux distribution a significant investment (read "big bucks") in time and money. If there ever were a situation where the "software money pit" could really take hold, it's in owning 30 million lines of constantly changing source code. Even in the simplest case, the development costs are typically in the millions of dollars, with the cost for the more comprehensive implementations substantially higher (Figure 2).

#### **Commercial Linux is** the answer

Where do we stand today on this debate? On the one hand, one could argue that the build-versus-buy Linux debate will take some time to decide because on one hand, engineers can just download Linux and go. On the other hand, the industry has matured overall, and there is certainly a better recognition of the real costs of developing software.

Accordingly, complexity and development costs have grown over the past several years and are significant factors when selecting an embedded operating system. We can safely conclude that if it made economic sense years ago to buy instead of create, which has played out in the RTOS environment, it overwhelmingly makes sense now when the move is being made to a far more capable but far more complex embedded Linux-based environment.

Jim Ready is a recognized authority in the embedded systems and real-time software industry. He founded MontaVista in 1999 to provide the Linux operating

system to the embedded systems market and to offer embedded-systems expertise to the open source Linux community. He received his BA in Physiological Psychology from the University of Illinois at Urbana-Champaign and his MA in Physiological Psychology from the University of California, Berkeley. For more information, email info@mvista.com.

> MontaVista Software 408-572-8000 www.mvista.com

#### **Develop-It-Yourself Linux Large-Scale Deployment**

Here's what it takes:

Based on a three-year project - at \$75/hr

Figure 2

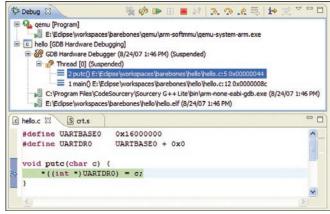

IDEs such as Eclipse Europa make life easier for embedded developers. Europa introduces several productivity enhancements, including a new version of Eclipse CDT that speeds up the creation of C/C++ projects, make code structures easier to understand, and simplifies setup of hardware debugging sessions.

Before the advent of Integrated Development Environments (IDEs), most embedded developers debugged software by writing information to the console or by using command-line, source-level debuggers such as gdb. Either way, it was difficult and time consuming to debug complex data structures. With a well-designed IDE, on the other hand, a developer can view data structures easily, using a point-and-click user interface. Moreover, the IDE can present a single interface for most development tasks, eliminating the need to constantly switch between editors, compilers, debuggers, and other tools. The net result: greater productivity.

A well-designed IDE may look simple on the outside, but underneath, it's a complex application. Building one requires considerable financial resources, a suitable architecture, a skilled workforce, and a lot of time. In fact, most software vendors don't have the resources to support an IDE on multiple hardware platforms, and even those who concentrate on a single platform struggle to keep pace with evolving customer requirements.

The Eclipse open source project addresses these problems. Software vendors and code contributors from a variety of sectors work together to create the Eclipse frameworks and IDEs, which vendors then use as the basis for their commercial development environments. As a result of this approach, vendors can focus on creating innovative, value-added tools, rather than on maintaining their own homegrown IDEs. The Eclipse C/C++ Development Tools (CDT) subproject is a prime example of the Eclipse

ecosystem in action. Created by several vendors working in concert, the CDT has quickly become the de facto standard for C and C++ development in the embedded industry. In fact, most RTOS and embedded tools vendors now base their IDEs on the CDT.

Until 2006, however, project teams at Eclipse generally released new versions of their components on independent schedules. This approach proved difficult for vendors that wanted to distribute products based on components from multiple projects. As a result, the Eclipse Foundation staff worked with the leaders of the most popular projects to coordinate project releases. The first simultaneous release of Eclipse projects, called *Callisto*, became available in June 2006; the second simultaneous release, called Europa, debuted in June 2007.

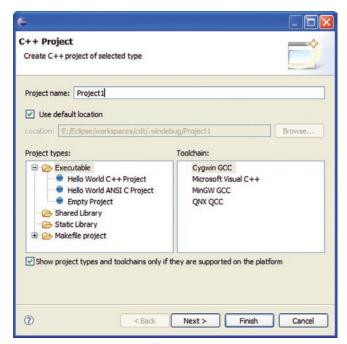

The Europa release includes the latest version of the CDT, version 4.0. (This is a milestone release for the CDT project, which celebrated its fifth anniversary this year.) When developing CDT 4.0, the CDT project team focused on streamlining the project creation experience for new users, making code structures more understandable, and simplifying the debugging process.

#### C/C++ project wizard simplifies creation

When users launch CDT 4.0, the first thing they see is an updated version of the New Project wizard (Figure 1). In previous releases, users had to select whether they were using C or C++; they also had to choose which CDT build system would build their projects. With CDT 4.0, the New Project wizard hides the details of the underlying build systems, simplifying the process of setting up and maintaining new projects.

In this wizard, the user selects the type of project (executable, shared library, static library, and so on) they are building as well as the toolchain that they will use to build it. Some project types also provide the option of using a project template to generate

Figure 1

build settings and skeletal source code. Choosing this option automates the preliminary work otherwise required to set up a new project for a given problem domain. In the past, users would have to set up a makefile, understand and decide on compiler command-line options, decide on the project's structure, figure out include paths, and then create all of this before writing the first C file.

If developers want to use their own makefile, they can choose Makefile projects. This new option is especially useful for embedded developers who need full control of their build steps; for example, to control linker scripts or build downloadable images. Makefile projects place almost no limitation on what can be done within the makefile (arbitrary commands, for example). IDE-built projects, in comparison, allow for simpler build scenarios: change a file, recompile, or update binaries. Anyone familiar with CDT will find the Makefile projects option similar to the old Standard Make projects. However, the Makefiles option allows the developer to specify which toolchain they are using for the build to assist the CDT when creating its source code index.

The other project types, for creating executables and shared and static libraries, automate control of the build process by using CDT's internal build system. By automating the build process, the New Project wizard frees users from having to create their own makefiles and allows them to focus on writing code.

Toolchain vendors are free to extend the New Project wizard as well. They can provide integrations for their toolchains, thereby allowing their users to take advantage of CDT's build automation features. Vendors can also add project types and templates that customize the CDT for their specific environments. For instance, a vendor could create a project type that generates boilerplate code for device driver projects.

#### Navigation, editing features increase viewing capabilities

One of the most useful features of the CDT is its internal parsers and source code indexing component. This functionality drives a number of the CDT's source navigation and editor features. The

### CONCURRENT SECTION TECHNOLOGIES

http://www.gocct.com Email: info@gocct.com Tel: (781) 933-5900

CDT editor now provides enhanced text coloring that highlights identifiers based on their role in the program. For example, it can use one color scheme to identify functions defined by the user and another color scheme to identify calls to functions from header files on the system include path.

A new call hierarchy view provides a tree view that shows function call relationships (Figure 2). Using this view, the user can see which functions call which other functions, without having to run and debug the application. The CDT also provides a similar view for viewing file inclusion relationships. It also provides an enhanced Type Hierarchy view to show C++ class hierarchies and the member variables and functions of those classes.

#### GDB hardware debugging

The CDT debugging component has always had an extensive integration with the GNU debugger, gdb. This debugger is very popular with embedded developers due to its free availability and support for a large variety of target architectures. JTAG/BDM vendors are also catching on to gdb's popularity. Thanks to gdb's built-in simple remote debugging protocol, it is possible to use gdb as a front-end for hardware debugging sessions. However, with previous releases of the CDT, it was very difficult to set up the CDT to use gdb with hardware debuggers.

To simplify the setup of hardware debugging sessions, CDT 4.0 introduces a debug launch configuration that lets the user enter a number of properties specific to using gdb for hardware

Figure 2

debugging. The launch configuration includes the remote address of the hardware debugger interface, the location of the image file, if necessary, as well as commands to customize the startup of the gdb session to prepare the embedded target for execution. In addition to CDT, the Eclipse Device Software Development Platform (DSDP) provides even more functionality to aid embedded developers (see sidebar).

#### A complete IDE for embedded development

Europa and the CDT/DSDP projects are providing complete support for developing C and C++ code for embedded systems

#### **Device software components**

The CDT addresses the general needs of C/C++ development and provides support for the edit, build, debug cycle of embedded development. The Eclipse Device Software Development Platform (DSDP) provides additional features that focus on the specific needs of embedded developers. For Europa, the DSDP project has also released a number of components that plug into the Eclipse environment. These include the Remote System Explorer, which provides a framework and tools for accessing remote targets. This framework allows the developer to transfer files to the target and to perform remote execution and debugging of applications. DSDP also provides a new terminal view for command-line access to remote targets, using telnet or ssh over serial or network connections.

Europa also provides a preview of the DSDP's device debugging component. This component is designed to handle the specific requirements of some embedded debugging environments and will be used by a number of vendors in future Eclipse releases.

Meanwhile, Eclipse continues to provide a strong foundation for building IDEs. A large number of vendors have caught onto this already and are building their commercial IDEs based on this platform. The QNX Momentics IDE is an example of this. It adds the necessary compilers and debuggers to build applications for the QNX Neutrino operating system. QNX also created their own proprietary Eclipse components to provide support for system and application profiling.

and additional components for embedded development. Europa is also making system developers' lives easier via simplified project creation, code structuring, and hardware debugging.

Many vendors are sharing in the work of the open source Eclipse platform as they build their own customizations to create successful commercial products. It is this sharing and commercialization that creates a healthy Eclipse ecosystem and ensures the continued evolution of Eclipse technologies to further meet the productivity needs of embedded developers.

Doug Schaefer is the project leader for the Eclipse CDT project and a tools architect for QNX Software Systems, where he is involved in all aspects of the QNX Momentics integrated development environment. He has been a tools developer for most of his career, having worked for ObjecTime, Rational, and IBM

building modeling tools for embedded systems. He is a strong proponent of open source software development and is heavily involved in Eclipse, not only leading the CDT project, but also as a member of the project management committee that oversees all tools projects at Eclipse. He can be reached at DSchaefer@gnx.com.

> **QNX Software Systems** 613-591-0931 www.qnx.com

Today, FPGAs are being used more often in a broad spectrum of applications. With their inherent attributes, they offer avionics design engineers advantages not available in ASIC-based platforms. FPGAs are susceptible to particle-induced Single-Event Upsets (SEUs). Combining the use of FPGAs and a structured ASIC provides a clear migration path for designers to utilize.

The use of FPGAs in many applications is rapidly increasing. With the attributes of reconfigurability and design-toworking part times much faster than those of ASICs, FPGAs offer avionics engineers advantages not available in maskprogrammable silicon platforms. However, SRAM-based FPGAs are susceptible to particle-induced SEUs, which make their deployment in avionics problematic. The solution to this dilemma lies in the use of both FPGAs and a structured ASIC for complete system development, with a clear migration path using a single tool flow and suite. Using an FPGA to validate an initial design and then migrating from the FPGA to a structured ASIC reduces cost, power, and system susceptibility to SEUs.

#### Atmospheric-induced SEUs

The atmosphere is the source of several types of ionizing subatomic particles that can interfere with the normal operation of electronic components. These particles are the result of solar rays and galactic cosmic rays that collide with the oxygen and nitrogen atoms in the Earth's atmosphere and produce high-energy protons and neutrons. Any of these particles have the potential to cause an SEU in an integrated circuit. NASA defines SEUs as "radiationinduced errors in microelectronic circuits

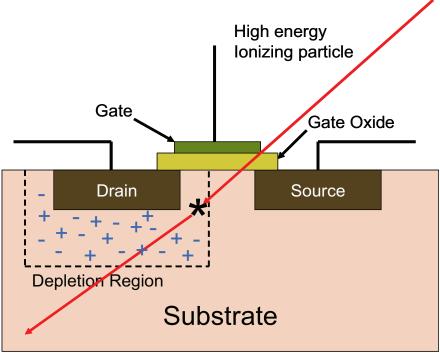

caused when charged particles (usually from the radiation belts or from cosmic rays) lose energy by ionizing the medium through which they pass, leaving behind a wake of electron-hole pairs."[1] Figure 1 illustrates high-energy particles from space passing through silicon. They produce hole-electron pairs that can change the state of a memory cell or the configuration bit of an FPGA.

The density or flux of neutron particles peaks at several tens of thousands of feet above the ground, often at levels where avionic equipment operates. Other particles such as secondary protons are also present, but for SEU effects, neutrons have the highest probability of interfering

with electronic system operation. The greatest density of these neutrons is at around 50,000 to 60,000 feet. Below that level, they are attenuated by the atmosphere, resulting in a much lower density at ground level. At 30,000 feet, a chip will have a Failure-In-Time (FIT) rate far higher than that at ground level.[2]

When a high-energy neutron impacts a transistor on a chip, potentially, the magnitude of the pulse may be sufficient to change the state of a logic node. This is called a soft error, since only data is affected, not the functionality of the circuitry. These errors are typically transient and are nondestructive when they occur in logic circuits. However, in a volatile

Figure 1

memory circuit or latch, such as an SRAM cell, the neutron impact may change the state of the memory, which can have consequences on the operation of the chip containing the affected memory cell.

For military and commercial missioncritical avionics applications in jet aircraft and other high-altitude vehicles, there are concerns about using SRAMbased FPGAs, because of the possibility of neutron-induced SEUs. In many cases, designers are forced to use ASICs or One-Time Programmable (OTP) devices that have density or performance limitations.

#### **SRAM-based FPGA circuit**

SRAM-based FPGAs have their functionality set by the bit pattern in an SRAM configuration memory. If an SEU upsets a configuration memory bit, the device's functionality can change, which may result in data corruption. The error, if not detected and corrected, can become a "hard" error. When an SEU-induced error is detected, the FPGA must be reconfigured, in some cases with the device's power turned off to clear the fault and then reapplied.

An FPGA's SRAM-based configuration memory, which controls the FPGA's logic and routing, is the part of the FPGA sensitive to SEUs. SEU-based configuration memory problems include modifying the chip's logic, disrupting interconnect paths, changing the global clocking, and modifying operation of the user I/O pins.

Configuration memory upsets can be detected and corrected using configuration feedback. This has led to different solutions at various cost levels, including making the SRAM cells more robust and introducing additional circuitry to support Error Correction Codes (ECCs), Triple Module Redundancy (TMR), and/or Cyclic Redundancy Code (CRC). Each of these has various pros and cons at the system level.

ECC support is provided by additional circuitry that stores the FPGA's configuration in additional bits in the memory word and calculates a checksum for the contents. This checksum is periodically compared to the checksum for the FPGA's configuration memory contents and, if a discrepancy is found, the FPGA is reconfigured. In a similar manner, extra circuitry can be used for CRC checking, to see if the configuration memory contents have changed. If they have, the FPGA is reconfigured, either partially or

**46** Using an FPGA to validate an initial design and then migrating from the FPGA to a structured ASIC reduces cost, power, and system susceptibility to SEUs. 77

fully, to reproduce the correct configuration memory pattern. The additional circuitry for ECC and CRC costs chip complexity, area, and power and also produces latency between the Soft Error Rate (SER) detection and correction.

TMR provides embedded "majority voting" circuits in flip-flops that result in high levels of tolerance to SEUs. If an error is detected the device must be reconfigured. TMR is hardwired into the design and results in significant additional silicon area, extra weight, additional power dissipation, and potentially reduced speed.

#### Migrating to a structured ASIC

Designers can customize SRAM-based FPGAs to application-specific algorithms for many high-altitude applications including flight control systems, displays, high-altitude electronic warfare systems, Unmanned Aerial Vehicles (UAVs), global positioning, seeker modules on missiles, and communications modules. FPGAs provide performance capabilities approaching those of ASICs and far beyond those offered by OTP devices such as UV EPROM, EEPROM, or antifusebased devices. SRAM-based FPGA vendors are also hardening devices to be more SEU tolerant.

However, designers can further reduce their development risk and improve time to market by initiating their designplanning efforts using an SRAM-based FPGA, validating the design in-system and at-speed, and then migrating from the FPGA to a structured ASIC with lower power, SEU immunity, and a single chip.

In a structured ASIC, metal interconnects replace all the configuration RAM elements, dramatically reducing the

probability of SEU-induced errors and the need for error mitigation for the configuration SRAM. Military applications need an ITAR tool flow to assure IP security during overseas manufacturing. Altera is in the process of supporting such an effort for overseas manufacturing. All metal lines are predefined and then programmed for a particular logic configuration using vias between the lines. A structured ASIC offers faster development and lower NRE costs than a standard-cell-based ASIC, as well as significantly lower unit cost and power, and often higher performance,

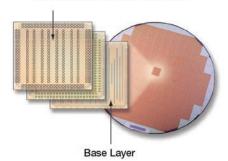

#### Standard-Cell ASIC: All Layers Are Custom

Full Set of Masks for Standard-Cell ASIC

#### Structured ASIC: **Customization Through Top Layers**

Figure 2

compared to a high-end FPGA, as illustrated in Figure 2. A structured ASIC also eliminates the programming circuitry associated with an FPGA.

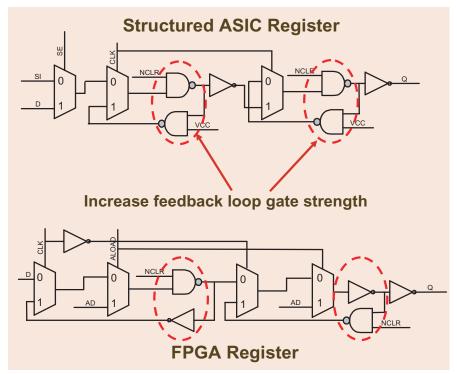

Registers are needed in any logic design and, like any nonvolatile element, they are susceptible to SEUs. Some older FPGAs have similar registers or latch SERs to what is found in an ordinary ASIC. Structured ASICs have architectural features to eliminate this problem and to improve overall soft error rates[3] over an FPGA:

- Increasing feedback loop gate strength

- Isolating the master and slave stages with an inverter

- Improving node capacitance via programming

- Not creating an asynchronous load MUX if it is not needed

The schematic in Figure 3 shows Altera's HardCopy II Structured ASICs implementation of logic features that are not available on an FPGA and how SEUs are reduced by adding logic to improve feedback loop gate strength.

These architectural features provide the highest level of DAL, Level A. Development Assurance Levels (DALs) are used within Aerospace Recommended Practices (ARPs) to classify system components based on their most severe failure condition associated with an aircraft-level function. DALs range from Level A failure is catastrophic - to Level E, where failure has no safety effect. At a 130 nm process node and 1.5 V, the structured ASIC has a neutron SER cross-section (> 10 MeV, sea-level) of 7E-15. For 90 nm and 1.2 V, using hardened register design, the neutron SER cross-section (> 10 MeV, sea-level) drops below 1E-15.

Figure 3

A well-designed structured ASIC also significantly reduces dynamic and static core power over an equivalent FPGA. For example, there are several ways to reduce static power:

- Removing the programming circuit and configuration logic

- Powering on only the logic and memory that the actual circuit uses

- Powering down the unused logic and memory with via connections

Unlike cell-based ASICs, structured ASICs can be quickly and easily manufactured with short fabrication cycles and low NRE charges for each design iteration.

#### Realizing design benefits using structured ASICs and FPGAs

Developing your system with a structured ASIC and an FPGA can provide identical functionality and performance during the finalization of the design algorithms, as observed in the lab with the FPGA-based prototype. Designers can be certain that they'll get a lower power, single-chip SEU-immune device without the need for an external storage device, the latter feature improving system reliability and reducing board space by eliminating a chip. A further benefit is that designers can switch back to an FPGA if they need to modify the design to accommodate a design change or target the chip for a different application.

#### References

- 1. NASA Aerospace Science and Technology Dictionary, http://www.hq nasa.gov/office/ hqlibrary/aerospacedicti nary/aerodictall/s.html.

- 2. Graham, Paul e al, "Consequences and Categories of SRAM FPGA Configuration SEUs," Los Alamos National Laboratory, Paper LA-UR-03-6122.

- 3 Euzent, Bruce et al, "Structured ASIC for SEU Mitigation of SRAM-based FPGAs," presented at the 2006 MAPLD International Conference, Washington DC, Sept. 26-28, 2006.

Amr El-Ashmawi is the senior marketing manager responsible for the military and aerospace business unit at Altera. He has more than 16 years of experience in

semiconductor design, programmable logic, and working within the environment of the defense market. Prior to joining Altera, Amr was the director of marketing at SiliconExpert Technologies, where he was a founder with responsibilities in providing component management tools to the commercial and defense industries. He has also held marketing and engineering positions at Actel Corporation. He holds a BSEE and MSEM from Santa Clara University. To learn more, contact Amr at aelashma@altera.com.

> Altera Corporation 408-544-7000 www.altera.com

#### **Systems:** Footlockers for military files

# Deployable mass storage systems: Bringing military applications to the front lines By Laura Cooper

Today's military and intelligence applications increasingly require deployability. This includes everything from mobile communications to data surveillance. The system requirements for many of these applications are demanding: high-performance processing, multiple I/O options, and massive storage. Yet many systems on the market today often fall short of fulfilling all of these requirements, and may only be somewhat portable, limiting their application uses. Today's laptops max out at dual core processing technology, limited I/O options, and about 4 GB of storage. Deployability of higher-performing systems, those capable of collecting, storing, and transmitting large amounts of sensitive data, is a request that is on the rise in the military and intelligence communities.

Massive storage alone is not a useable component in a system that does not also incorporate those features an all-in-one mobile system should provide. Powerful processors and multiple I/O are needed to fully utilize the application capabilities of a system capable of storing seismic amounts of data.

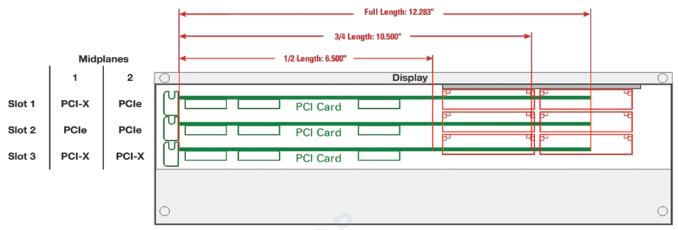

A deployable mass storage system is one that is capable of housing loads of data, yet small enough that it is portable. For this feat to be possible, the system also must utilize advanced processing technology and I/O options such as the several PCI or PCIe slots. In effect, the system is a portable computer system that performs various tasks, ideally suited for gathering, storing, and disseminating large amounts of critical data out in the field, in a laboratory, or virtually anywhere. As technology advances, the development of systems offering massive storage in a deployable form factor, coupled with the performance and I/O needed to utilize it, mobilizes mission-critical applications that once could not be taken into the field.

#### Sensitive information collection, storage, and dissemination

Military intelligence is information needed to plan for our national defense. Knowledge of the number, location, and tactics of enemy forces and potential battle areas is needed to develop military plans. To acquire information, services and agencies rely on aerial photographs, electronic monitoring, data gathering, and human observation. Intelligence specialists collect and study the information required to design defense plans, strategy, and tactics.

The methods utilized to gather tactical information are at the forefront of technology, enabling data streaming at speedy rates to ensure information is as close to real time as possible. A mobile system that provides enough processing power, I/O options, and storage for the large amounts of data being gathered would speed up the collection process and foster truer analytical results. Most, if not all, data gathering applications of this type require more than 4 GB of storage, more than most laptops can provide. A portable system with high storage capacity, perhaps even up to 2 TB, would be ideal.

#### System requirements for information collection

There are three elements required in a system used for information gathering and transmittance, a function technically referred to as high-throughput data streaming.

The first is the availability of numerous high-speed hard drives. The number of drives is relative to the speed of data transfer, and the more drives there are, the faster the transfer rate is. Hard drive options in smaller form factors have emerged in the form of 2.5" drives, proven to be as robust and reliable as 3.5" drives. These smaller drives allow for the chassis to be smaller, and hence, more portable. Figure 1 illustrates potential hard drive configurations in a portable form factor.

Secondly, powering many high-speed drives requires the performance of top-of-the-line processor cores. AMD and Intel workstation class processors, including each company's respective implementations of quad core processing, would provide the boost needed to maximize throughput rates.

Finally, several high-performance PCI or PCIe slots enable application-specific cards to perform data transfer, sniffing, and collection. Some examples relevant to deployed, military/ intelligence applications include MIL-STD-1553, NTDS, DSP cards, Fibre Channel, and other FPGA powered I/O cards. Ideally, a system would utilize open standards, easily capable of accommodating all of these types of cards and many others.

The ability to house large amounts of storage in a deployable computer system would enable a variety of uses for smaller systems. A system of this type could be used as a portable sniffer, enabling on-site troubleshooting for many intelligence applications where a data center or laboratory is not accessible. A portable data recorder, with lots of storage, would enable the

Figure 1

collection of real-time data of any type (video, audio, communication signals, or encrypted code) for on-site or later analysis.

Ideally, a system utilized for these applications would incorporate the latest in quad core processing, up to four PCI or PCIe slots, and allow for as many as 15-18 HDDs to be utilized. If capacities for each drive reach the current standard for a 2.5" drive, each would house up to 200 GB. In addition, a user interface with integrated screen and keyboard/mouse would foster ease of use. Some computer designers have begun to implement the technology in smaller chassis to allow maximum storage in a deployable form factor.

#### Mobile information collection and military apps

But which military intelligence agencies could utilize a deployable system with loads of storage, powerful processors, and multiple I/O? And what would they use it for? The choices are so vast that only a few are listed here.

#### **SIGINT**

SIGnals INTelligence (SIGINT) is used in missions to intercept and analyze foreign adversaries' communications signals, many of which are protected by codes and other complex countermeasures. They collect, process, and disseminate reports on foreign intelligence targets in response to requirements set at the highest levels of government. A deployable computer capable of high-speed data and signal collection and analysis would allow closer to real-time results from the outset. Sensitive information, such as that relayed by SIGINT, is more accurate the more quickly it is received. Collection of the data out in the field utilizing a deployable collection system would speed up the entire dissemination process.

#### C4ISR

Command, Control, Communication, Computer, Information, Surveillance, and Reconnaissance (C4ISR) missions have become increasingly deployable, utilizing portable technology on humvees and in tents, for example. The transmission of sensitive information in these applications would also benefit from a truly deployable mass storage system, rendering truer analysis results from communications brought as close to real time as possible.

#### **TAMPS**

The Tactical Aircraft Mission Planning System (TAMPS) is a computer-based method for weapons planning and optimizing mission routes against hostile targets. TAMPS is designed to provide a common automated system for rapidly processing large quantities of digitized terrain, threat, and environmental data, along with aircraft, avionics, and weapon systems parameters that assist in the precision engagement of enemy forces. TAMPS would benefit greatly from a deployable mass storage device to process and transmit various sorts of data. The system would ideally take up minimal space in the aircraft and be transportable from one spot to another in a scenario like the one shown in Figure 2.

Figure 2

#### Mobile TOCs